#### Chapter 3

Professor Brendan Morris, SEB 3216, <u>brendan.morris@unlv.edu</u> http://www.ee.unlv.edu/~b1morris/cpe100/

#### **CPE100: Digital Logic Design I**

Section 1004: Dr. Morris Sequential Logic Design

# Chapter 3 :: Topics

- Introduction

- Latches and Flip-Flops

- Synchronous Logic Design

- Finite State Machines

- Timing of Sequential Logic

- Parallelism

#### Introduction

- Previously, Combinational Logic design had outputs only depend on current value of inputs

- Outputs of sequential logic depend on current and prior input values – it has *memory*.

- Some definitions:

- State: all the information about a circuit necessary to explain its future behavior

- Latches and flip-flops: state elements that store one bit of state

- Synchronous sequential circuits: combinational logic followed by a bank of flip-flops

# Sequential Circuits

- Give sequence to events (i.e. a notion of time)

- Have memory (short-term)

- Use feedback from output to input to store information

- Need to "remember" past output

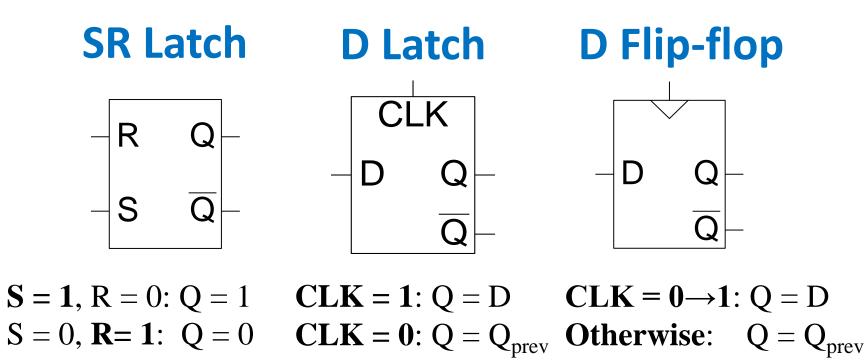

#### State Elements

- The state of a circuit influences its future behavior

- State elements store state

- Bistable circuit

- SR Latch

- D Latch

- D Flip-flop

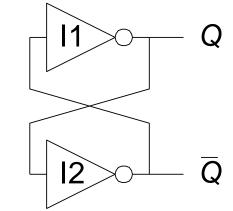

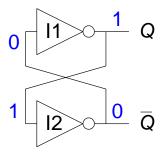

#### Bistable Circuit

- Fundamental building block of other state elements

- Two outputs:  $Q, \overline{Q}$  (state)

- No inputs

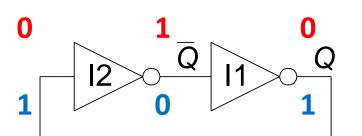

# Redrawn circuit to emphasize symmetry

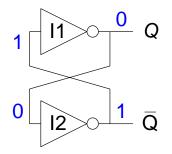

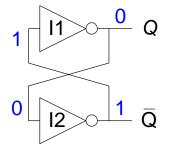

#### **Bistable Circuit Analysis**

- Consider the two possible cases:

- Q = 0: then  $\overline{Q} = 1$ , Q = 0 (consistent)

#### **Bistable Circuit Analysis**

- Consider the two possible cases:

- Q = 0: then  $\overline{Q} = 1$ , Q = 0 (consistent)

• Q = 1: then  $\overline{Q} = 0$ , Q = 1 (consistent)

- Stores 1 bit of state in the state variable, Q (or  $\overline{Q}$ )

- But there are **no inputs to control the state**

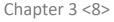

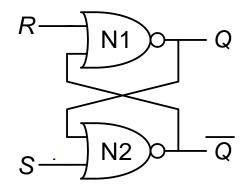

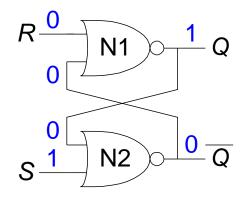

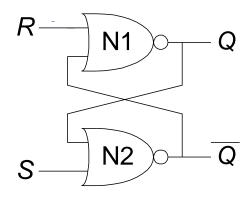

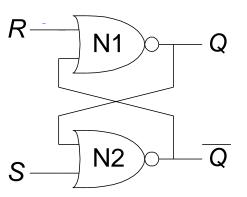

# SR (Set/Reset) Latch

- SR Latch

- S set Q=1

- R reset Q = 0

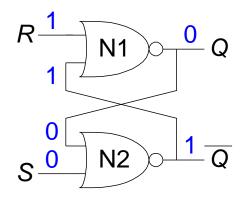

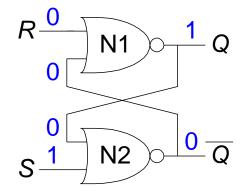

### SR (Set/Reset) Latch

• SR Latch

- Consider the four possible cases:

- S = 1, R = 0

- S = 0, R = 1

- S = 0, R = 0

- S = 1, R = 1

• S = 1, R = 0:

then Q = 1 and  $\overline{Q} = 0$

© Digital Design and Computer Architecture, 2<sup>nd</sup> Edition, 2012

Chapter 3 <11>

• S = 1, R = 0:

then Q = 1 and  $\overline{Q} = 0$

*S* = 1, *R* = 0:

then

$$Q = 1$$

and  $\overline{Q} = 0$

•

$$S = 0, R = 1$$

:

then  $Q = 0$  and  $\overline{Q} = 1$

© *Digital Design and Computer Architecture*, 2<sup>nd</sup> Edition, 2012

Chapter 3 <13>

• S = 1, R = 0:

- then Q = 1 and  $\overline{Q} = 0$

- Set the output

• S = 0, R = 1: then Q = 0 and  $\overline{Q} = 1$ *Reset* the output

S = 0, R = 0:

then

$$Q = Q_{prev}$$

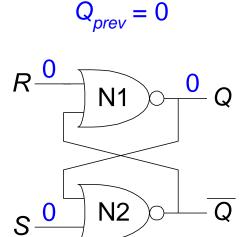

S = 0, R = 0:  $Q_{prev} = 0$  $Q_{prev} = 1$ then  $Q = Q_{prev}$ R\_\_\_\_  $R^{-0}$ \_\_\_\_Q N1 N1 Q - **Q** s<u> </u> s\_\_\_\_ N2 N2 Q

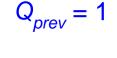

S = 0, R = 0:  $Q_{prev} = 0$  $Q_{prev} = 1$ R\_\_\_\_  $R^{-0}$ then  $Q = Q_{prev}$ \_\_\_\_Q N1 Q N1 - Q <u>s</u>\_0 S\_0 N2 N2 Q *S* = 1, *R* = 1:  $R^{\cdot}$ **N1** Q then Q = 0, Q = 0Q N2 S

S = 0, R = 0:  $Q_{prev} = 0$  $Q_{prev} = 1$ R<mark>\_0</mark>  $R^{-0}$ then  $Q = Q_{prev}$ \_\_\_\_Q N1 N1 Q - Q <u>s</u>\_0 S\_0 N2 N2  $\overline{O}$ *S* = 1, *R* = 1:  $R^{-}$ <mark>0</mark> Q N1 0 then Q = 0, Q = 0<u>0</u>\_Q N2 S.

© Digital Design and Computer Architecture, 2<sup>nd</sup> Edition, 2012

Chapter 3 <18>

- S = 0, R = 0:

- then  $Q = Q_{prev}$ Memory!

•

$$S = 1, R = 1$$

:

then  $Q = 0, \overline{Q} = 0$

Invalid State

$\overline{Q} \neq \text{NOT } Q$

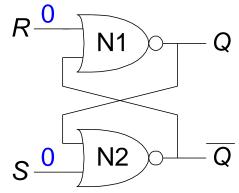

# SR Latch Symbol

- SR stands for Set/Reset Latch

- Stores one bit of state (Q)

- Control what value is being stored with *S*, *R* inputs

- Set: Make the output 1

$$(S = 1, R = 0, Q = 1)$$

- **Reset:** Make the output 0

- (S = 0, R = 1, Q = 0)

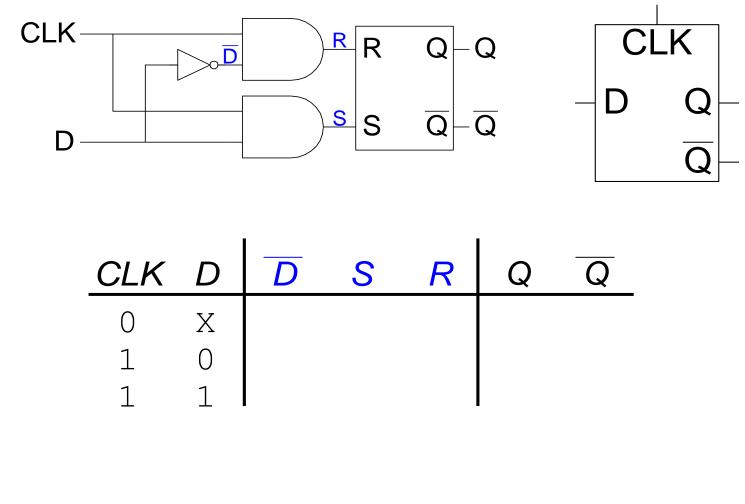

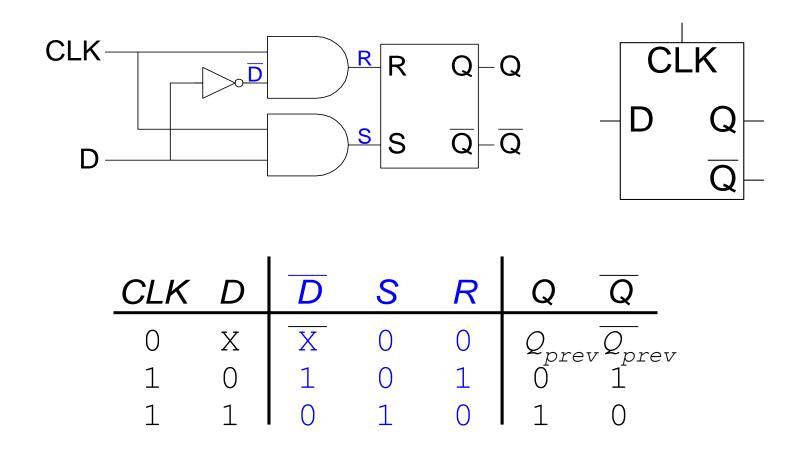

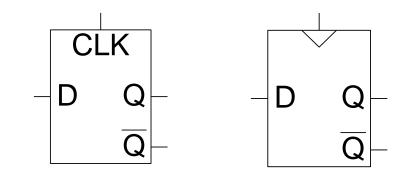

# D Latch

- Two inputs: *CLK*, *D*

- *CLK*: controls *when* the output changes

- **D** (the data input): controls *what* the output changes to

- Function

- When CLK = 1,

- *D* passes through to *Q* (*transparent*)

- When CLK = 0,

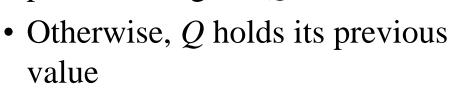

- Q holds its previous value (opaque)

- Avoids invalid case when  $Q \neq \text{NOT } \overline{Q}$

$\ensuremath{\mathbb{C}}$  Digital Design and Computer Architecture,  $2^{nd}$  Edition, 2012

**D** Latch

**Symbol**

CLK

D

### D Latch Internal Circuit

#### D Latch Internal Circuit

© Digital Design and Computer Architecture, 2<sup>nd</sup> Edition, 2012

Chapter 3 <23>

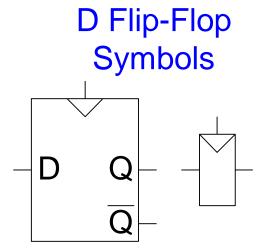

# D Flip-Flop

- Inputs: CLK, D

- Function

- Samples D on rising edge of CLK

- When *CLK* rises from 0 to 1, *D* passes through to *Q*

- *Q* changes only on rising edge of *CLK*

- Called *edge-triggered*

- Activated on the clock edge

© Digital Design and Computer Architecture, 2<sup>nd</sup> Edition, 2012

Chapter 3 <24>

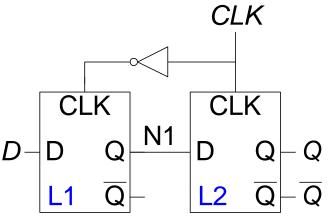

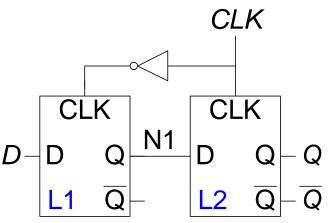

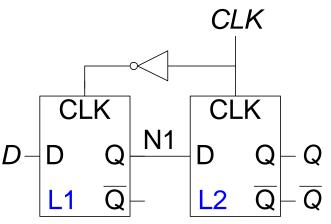

# D Flip-Flop Internal Circuit

- Two back-to-back latches (L1 and L2) controlled by complementary clocks

- When CLK = 0

- L1 is transparent

- L2 is opaque

- D passes through to N1

# D Flip-Flop Internal Circuit

- Two back-to-back latches (L1 and L2) controlled by complementary clocks

- When CLK = 0

- L1 is transparent

- L2 is opaque

- D passes through to N1

- When CLK = 1

- L2 is transparent

- L1 is opaque

- N1 passes through to Q

# D Flip-Flop Internal Circuit

- Two back-to-back latches (L1 and L2) controlled by complementary clocks

- When CLK = 0

- L1 is transparent

- L2 is opaque

- D passes through to N1

- When CLK = 1

- L2 is transparent

- L1 is opaque

- N1 passes through to Q

- Thus, on the edge of the clock (when *CLK* rises from  $0 \rightarrow 1$ )

- D passes through to Q

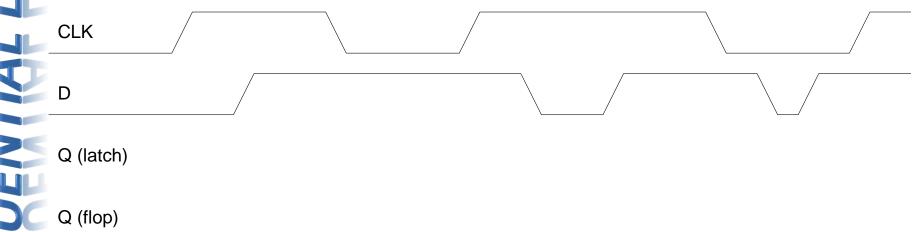

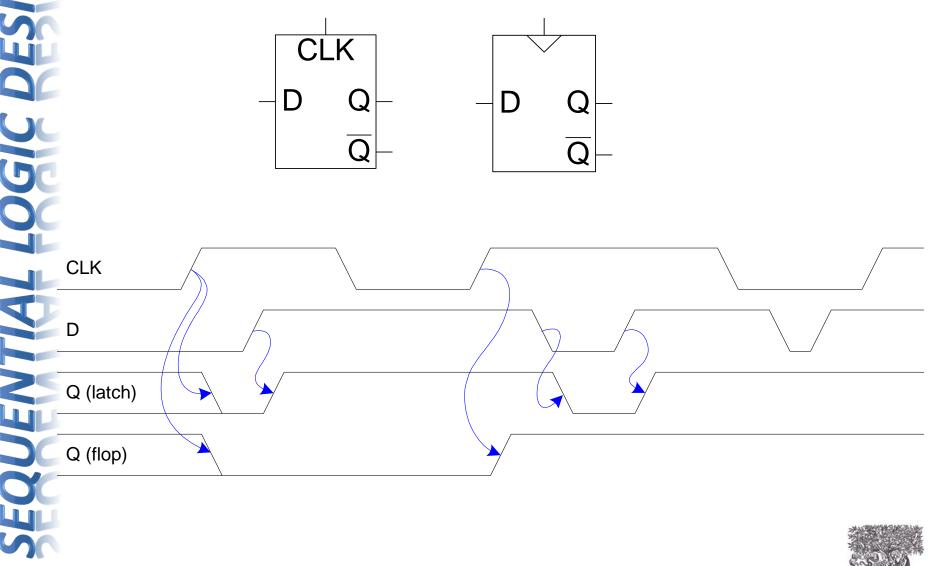

### D Latch vs. D Flip-Flop

© Digital Design and Computer Architecture, 2<sup>nd</sup> Edition, 2012

Chapter 3 <28>

# D Latch vs. D Flip-Flop

ELSEVI

#### Review

© Digital Design and Computer Architecture, 2<sup>nd</sup> Edition, 2012

Chapter 3 < 30>

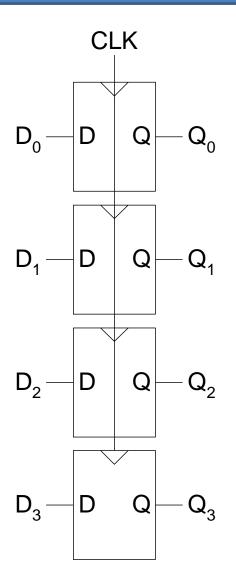

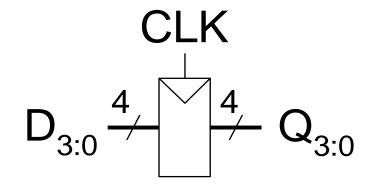

#### Registers

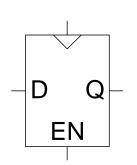

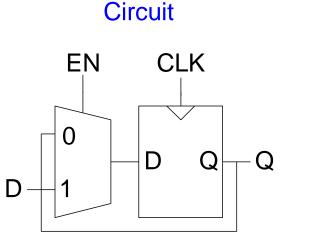

# **Enabled Flip-Flops**

- Inputs: CLK, D, EN

- The enable input (EN) controls when new data (D) is stored

- Function

- EN = 1: D passes through to Q on the clock edge

- EN = 0: the flip-flop retains its previous state

Symbol

# **Enabled Flip-Flops**

- Inputs: CLK, D, EN

- The enable input (EN) controls when new data (D) is stored

- Function

- EN = 1: D passes through to Q on the clock edge

- EN = 0: the flip-flop retains its previous state

Internal

$\ensuremath{\mathbb{C}}$  Digital Design and Computer Architecture,  $2^{nd}$  Edition, 2012

Symbol

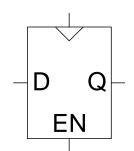

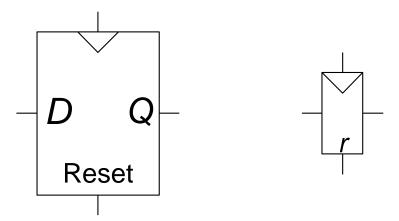

# **Resettable Flip-Flops**

- Inputs: CLK, D, Reset

- Function:

- **Reset** = 1: Q is forced to 0

- *Reset* = 0: flip-flop behaves as ordinary D flip-flop

# **Resettable Flip-Flops**

- Two types:

- Synchronous: resets at the clock edge only

- **Asynchronous:** resets immediately when *Reset* = 1

- Asynchronously resettable flip-flop requires changing the internal circuitry of the flip-flop

- Synchronously resettable flip-flop?

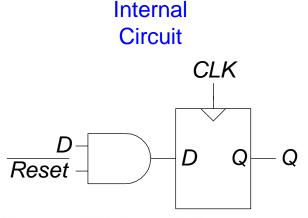

#### **Resettable Flip-Flops**

- Two types:

- Synchronous: resets at the clock edge only

- **Asynchronous:** resets immediately when *Reset* = 1

- Asynchronously resettable flip-flop requires changing the internal circuitry of the flip-flop

- Synchronously resettable flip-flop?

Chapter 3 <36>

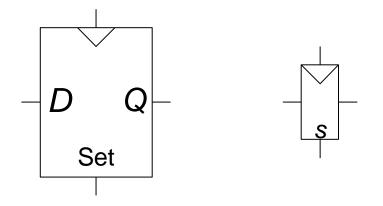

## Settable Flip-Flops

#### Inputs: CLK, D, Set

#### • Function:

- **Set** = 1: Q is set to 1

- *Set* = 0: the flip-flop behaves as ordinary D flip-flop

#### Symbols

#### Synchronous Sequential Logic Design

- Registers inserted between combinational logic

- Registers contain state of the system

- State changes at clock edge: system synchronized to the clock

#### Synchronous Sequential Logic Design

- **Rules** of synchronous sequential circuit composition:

- Every circuit element is either a register or a combinational circuit

- At least one circuit element is a register

- All registers receive the same clock signal

- Every cyclic path contains at least one register

#### Synchronous Sequential Logic Design

- **Rules** of synchronous sequential circuit composition:

- Every circuit element is either a register or a combinational circuit

- At least one circuit element is a register

- All registers receive the same clock signal

- Every cyclic path contains at least one register

- Two common synchronous sequential circuits

- Finite State Machines (FSMs)

- Pipelines

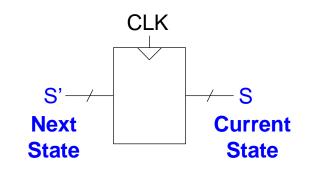

## Finite State Machine (FSM)

- Consists of:

- -State register

- Stores current state

• Loads next state at clock edge

#### - Combinational logic

- Computes the next state

- Computes the outputs

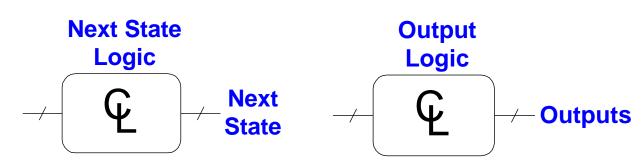

## Finite State Machines (FSMs)

- Next state determined by current state and inputs

- Two types of finite state machines differ in output logic:

- Moore FSM: outputs depend only on current state

- Mealy FSM: outputs depend on current state *and* inputs

Moore FSM

# ELSEVIER

$\ensuremath{\mathbb{C}}$  Digital Design and Computer Architecture,  $2^{nd}$  Edition, 2012

- . Identify inputs and outputs

- 2. Sketch state transition diagram

- . Write state transition table

- . Select state encodings

- . Rewrite state transition table with state encodings

- 5. Write output table

- Write Boolean equations for next state and output logic

- S. Sketch the circuit schematic

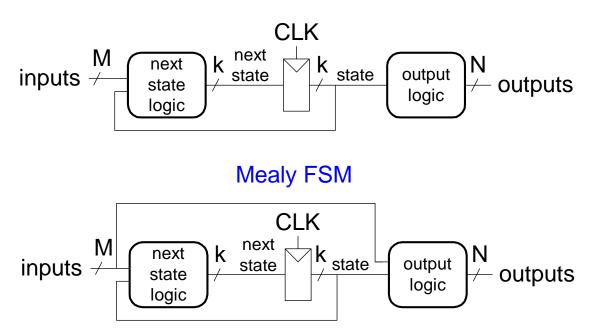

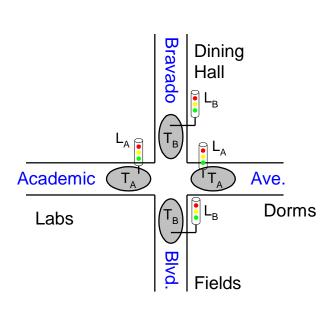

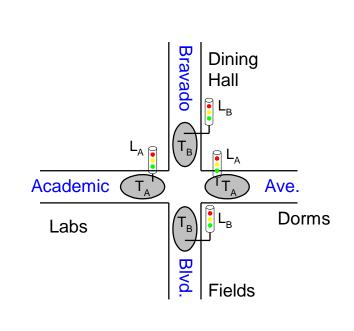

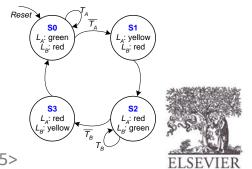

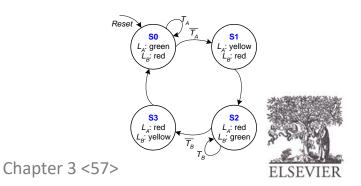

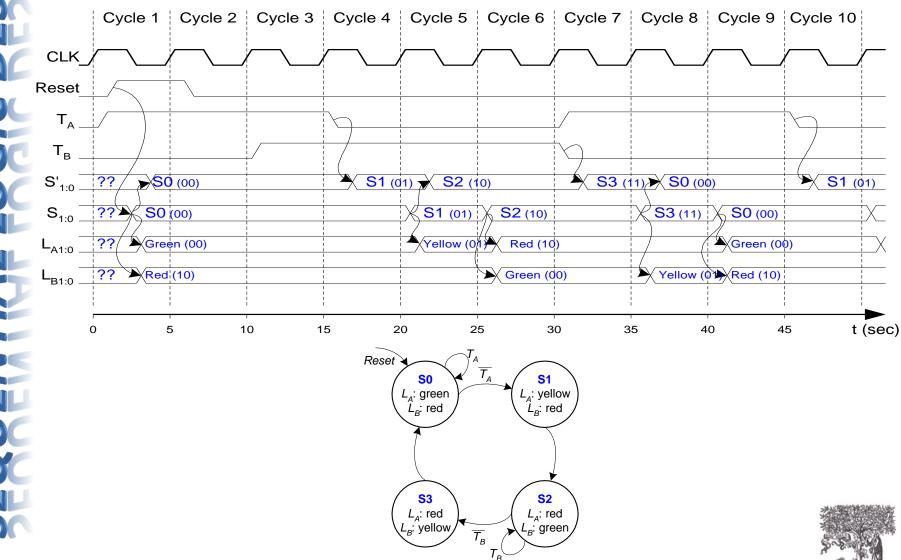

## FSM Example

- Lights:  $L_A, L_B$

- Traffic light controller

- Traffic sensors:  $T_A$ ,  $T_B$  (TRUE when there's traffic)

- . Identify inputs and outputs

- 2. Sketch state transition diagram

- Write state transition table

- . Select state encodings

- . Rewrite state transition table with state encodings

- 5. Write output table

- Write Boolean equations for next state and output logic

- S. Sketch the circuit schematic

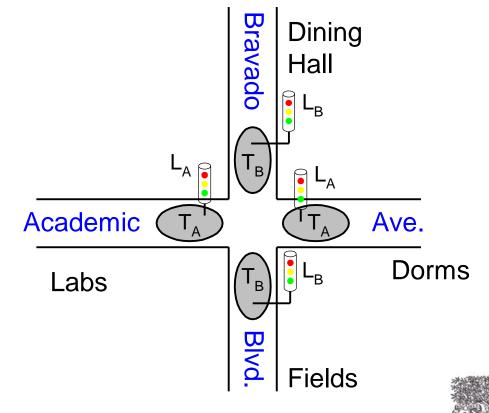

#### FSM Black Box

- Inputs: *CLK*, *Reset*,  $T_A$ ,  $T_B$

- Outputs:  $L_A$ ,  $L_B$

- . Identify inputs and outputs

- 2. Sketch state transition diagram

- Write state transition table

- . Select state encodings

- . Rewrite state transition table with state encodings

- 5. Write output table

- Write Boolean equations for next state and output logic

- . Sketch the circuit schematic

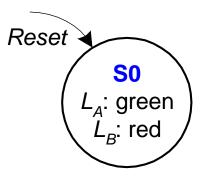

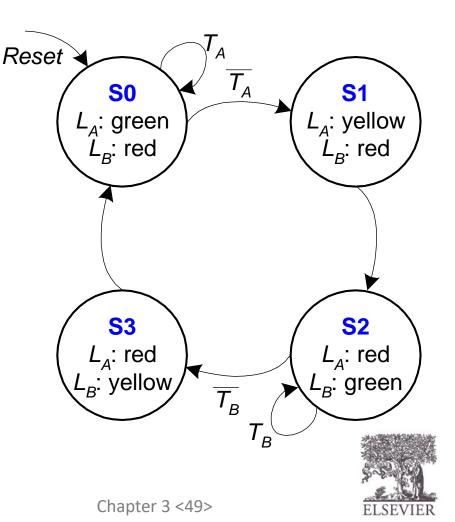

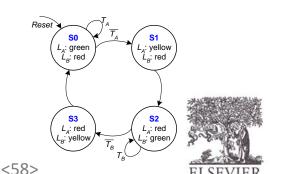

## FSM State Transition Diagram

- Moore FSM: outputs labeled in each state

- States: Circles

- Transitions: Arcs

## FSM State Transition Diagram

- Moore FSM: outputs labeled in each state

- States: Circles

- Transitions: Arcs

- . Identify inputs and outputs

- 2. Sketch state transition diagram

- . Write state transition table

- Select state encodings

- . Rewrite state transition table with state encodings

- 5. Write output table

- Write Boolean equations for next state and output logic

- . Sketch the circuit schematic

#### FSM State Transition Table

| Current<br>State | Inp   | Next<br>State |    |

|------------------|-------|---------------|----|

| S                | $T_A$ | $T_B$         | S' |

| SO               | 0     | Х             |    |

| <b>S</b> 0       | 1     | X             |    |

| <b>S</b> 1       | Х     | X             |    |

| S2               | Х     | 0             |    |

| S2               | Х     | 1             |    |

| <b>S</b> 3       | Х     | X             |    |

#### FSM State Transition Table

| Current<br>State | Inp   | Next<br>State |            |

|------------------|-------|---------------|------------|

| S                | $T_A$ | $T_B$         | S'         |

| <b>S</b> 0       | 0     | X             | <b>S</b> 1 |

| S0               | 1     | X             | <b>S</b> 0 |

| <b>S</b> 1       | Х     | X             | S2         |

| S2               | Х     | 0             | <b>S</b> 3 |

| S2               | Х     | 1             | S2         |

| <b>S</b> 3       | Х     | X             | <b>S</b> 0 |

- . Identify inputs and outputs

- 2. Sketch state transition diagram

- Write state transition table

- Select state encodings

- Rewrite state transition table with state encodings

- 5. Write output table

- 7. Write Boolean equations for next state and output logic

- S. Sketch the circuit schematic

#### FSM Encoded State Transition Table

| Y | Current State |                | ent State Inputs |       | Next State              |                         |   |      |

|---|---------------|----------------|------------------|-------|-------------------------|-------------------------|---|------|

|   | $S_1$         | S <sub>0</sub> | $T_A$            | $T_B$ | <i>S</i> ′ <sub>1</sub> | <i>S</i> ′ <sub>0</sub> |   | Sta  |

|   | 0             | 0              | 0                | X     |                         |                         |   |      |

| C | 0             | 0              | 1                | X     |                         |                         |   | S    |

|   | 0             | 1              | X                | X     |                         |                         |   | S    |

|   | 1             | 0              | X                | 0     |                         |                         |   | Sź   |

|   | 1             | 0              | X                | 1     |                         |                         |   | S.   |

|   | 1             | 1              | X                | X     |                         |                         | T | wo b |

| C |               |                |                  |       |                         |                         | - | F    |

| State      | Encoding |

|------------|----------|

| <b>S</b> 0 | 00       |

| <b>S</b> 1 | 01       |

| <b>S</b> 2 | 10       |

| <b>S</b> 3 | 11       |

Two bits required for 4 states

Reset S0  $L_{a}$ ; green  $T_{A}$  S1  $L_{b}$ ; vellow  $L_{b}$ ; red  $L_{$

© Digital Design and Computer Architecture, 2<sup>nd</sup> Edition, 2012

Chapter 3 <54>

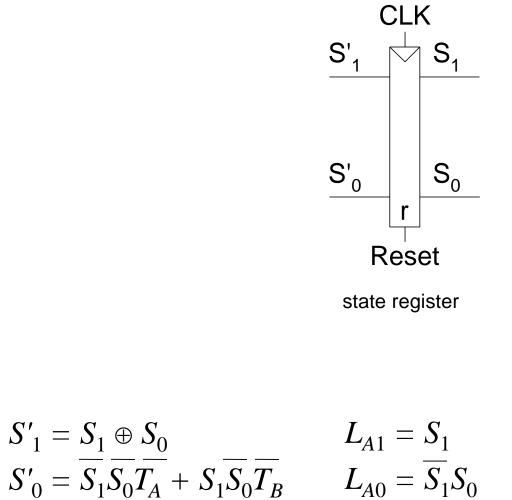

### FSM Encoded State Transition Table

| Curren                                    | Current State                                                                                                                            |       | Inputs |                         | Next State              |       |

|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-------|--------|-------------------------|-------------------------|-------|

| <i>S</i> <sub>1</sub>                     | S <sub>0</sub>                                                                                                                           | $T_A$ | $T_B$  | <i>S</i> ′ <sub>1</sub> | <i>S</i> ′ <sub>0</sub> | Sta   |

| 0                                         | 0                                                                                                                                        | 0     | X      | 0                       | 1                       |       |

| 0                                         | 0                                                                                                                                        | 1     | X      | 0                       | 0                       |       |

| 0                                         | 1                                                                                                                                        | Х     | X      | 1                       | 0                       | S     |

| 1                                         | 0                                                                                                                                        | Х     | 0      | 1                       | 1                       | S     |

| 1                                         | 0                                                                                                                                        | X     | 1      | 1                       | 0                       | S     |

| 1                                         | 1                                                                                                                                        | X     | X      | 0                       | 0                       | Two b |

| $S'_{\cdot} - S_{\cdot} \oplus S_{\cdot}$ |                                                                                                                                          |       |        |                         |                         |       |

|                                           | $S'_{1} = S_{1} \oplus S_{0}$<br>$S'_{0} = \overline{S_{1}} \overline{S_{0}} \overline{T_{A}} + S_{1} \overline{S_{0}} \overline{T_{B}}$ |       |        |                         |                         |       |

| © Digital Design and | Computer Architecture, | 2 <sup>nd</sup> Edition, 2012 |

|----------------------|------------------------|-------------------------------|

|----------------------|------------------------|-------------------------------|

| State      | Encoding |

|------------|----------|

| <b>S</b> 0 | 00       |

| <b>S</b> 1 | 01       |

| <b>S</b> 2 | 10       |

| <b>S</b> 3 | 11       |

Two bits required for 4 states

Chapter 3 <55>

- . Identify inputs and outputs

- 2. Sketch state transition diagram

- Write state transition table

- Select state encodings

- . Rewrite state transition table with state encodings

- . Write output table

- Write Boolean equations for next state and output logic

- Sketch the circuit schematic

## FSM Output Table

| Current State         |                | Outputs  |          |          |          |

|-----------------------|----------------|----------|----------|----------|----------|

| <i>S</i> <sub>1</sub> | S <sub>0</sub> | $L_{A1}$ | $L_{A0}$ | $L_{B1}$ | $L_{B0}$ |

| 0                     | 0              |          |          |          |          |

| 0                     | 1              |          |          |          |          |

| 1                     | 0              |          |          |          |          |

| 1                     | 1              |          |          |          |          |

| Output | Encoding |

|--------|----------|

| green  | 00       |

| yellow | 01       |

| red    | 10       |

Two bits required for 3 outputs

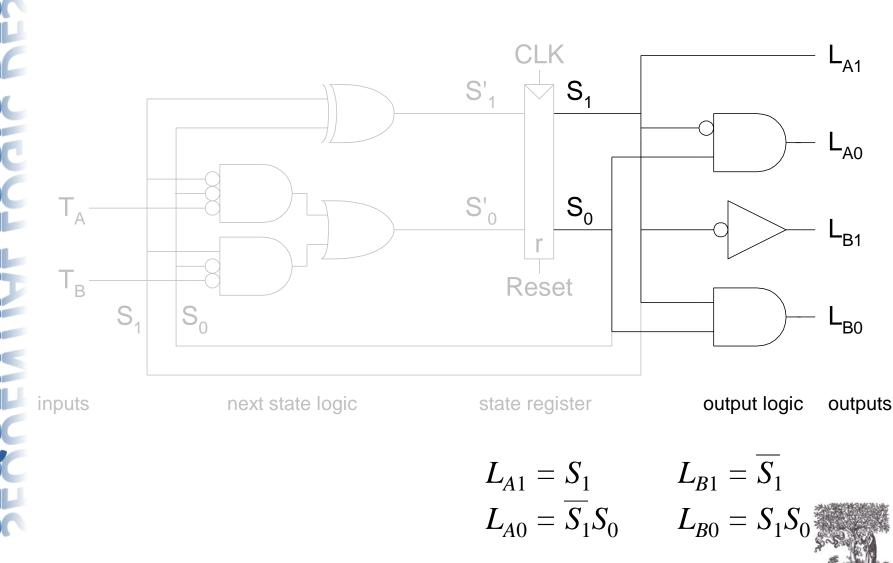

## FSM Output Table

| Current State  |                                             |          |          |          |          |  |

|----------------|---------------------------------------------|----------|----------|----------|----------|--|

| $S_1$          | S <sub>0</sub>                              | $L_{A1}$ | $L_{A0}$ | $L_{B1}$ | $L_{B0}$ |  |

| 0              | 0                                           | 0        | 0        | 1        | 0        |  |

| 0              | 1                                           | 0        | 1        | 1        | 0        |  |

| 1              | 0                                           | 1        | 0        | 0        | 0        |  |

| 1              | 1                                           | 1        | 0        | 0        | 1        |  |

| $L_{A1} = S_1$ |                                             |          |          |          |          |  |

|                | $L_{A1} = S_1$ $L_{A0} = \overline{S_1}S_0$ |          |          |          |          |  |

$L_{B1} = S_1$

$L_{B0} = S_1 S_0$

| Output | Encoding |

|--------|----------|

| green  | 00       |

| yellow | 01       |

| red    | 10       |

Two bits required for 3 outputs

© Digital Design and Computer Architecture, 2<sup>nd</sup> Edition, 2012

Chapter 3 <58>

- . Identify inputs and outputs

- 2. Sketch state transition diagram

- Write state transition table

- . Select state encodings

- . Rewrite state transition table with state encodings

- 5. Write output table

- Write Boolean equations for next state and output logic

- . Sketch the circuit schematic

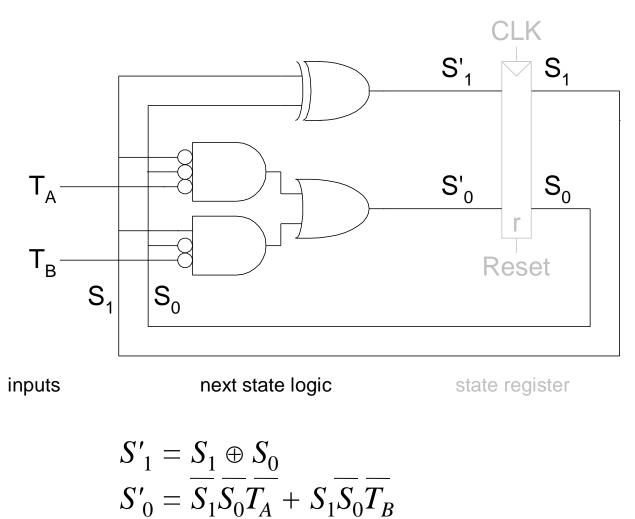

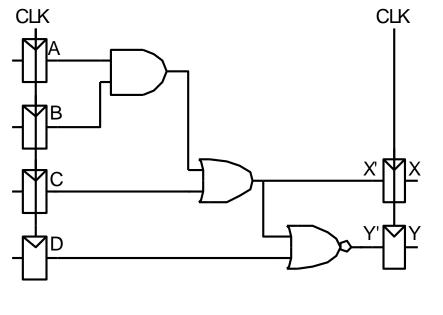

#### **FSM Schematic: State Register**

$$L_{A1} = S_1$$

$$L_{A0} = \overline{S_1}S_0$$

$$L_{B1} = \overline{S_1}$$

$$L_{B0} = S_1 S_0$$

© Digital Design and Computer Architecture, 2<sup>nd</sup> Edition, 2012

Chapter 3 <60>

#### FSM Schematic: Next State Logic

#### FSM Schematic: Output Logic

© Digital Design and Computer Architecture, 2<sup>nd</sup> Edition, 2012

Chapter 3 <62>

ELSEVIER

## FSM Timing Diagram

© Digital Design and Computer Architecture, 2<sup>nd</sup> Edition, 2012

Chapter 3 <63>

ELSEVIER

## FSM State Encoding

- **Binary** encoding:

- i.e., for four states, 00, 01, 10, 11

- One-hot encoding

- One state bit per state

- Only one state bit HIGH at once

- i.e., for 4 states, 0001, 0010, 0100, 1000

- Requires more flip-flops

- Often next state and output logic is simpler

- . Identify inputs and outputs

- 2. Sketch state transition diagram

- . Write state transition table

- . Select state encodings

- . Rewrite state transition table with state encodings

- 5. Write output table

- Write Boolean equations for next state and output logic

- S. Sketch the circuit schematic

## FSM Problems

- 1. Design a circuit to detect 3 or more 1's in a row in a bit stream

- 2. Vending machine: Release an item after receiving 15 cents

- Single coin slot but tells if you put in dime or nickel

- No change given

- 1. Identify inputs and outputs

- 2. Sketch state transition diagram

- 3. Write state transition table

- 4. Select state encodings

- 5. Rewrite state transition table with state encodings

- 6. Write output table

- 7. Write Boolean equations for next state and output logic

- 8. Sketch the circuit schematic

## Timing

- Flip-flop samples *D* at clock edge

- *D* must be stable when sampled

- Similar to a photograph, *D* must be stable around clock edge

- Moving right before or after shutter click results in blurry photo

- If not, metastability can occur

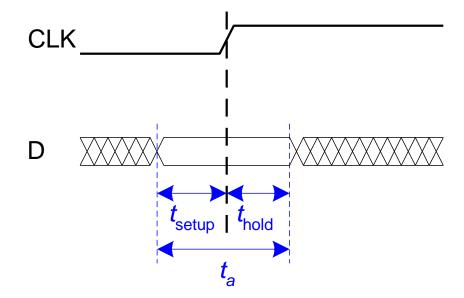

## Input Timing Constraints

- Setup time:  $t_{setup}$  = time *before* clock edge data must be stable (i.e. not changing)

- Hold time:  $t_{hold}$  = time *after* clock edge data must be stable

- Aperture time:  $t_a$  = time *around* clock edge data must be stable ( $t_a = t_{setup} + t_{hold}$ )

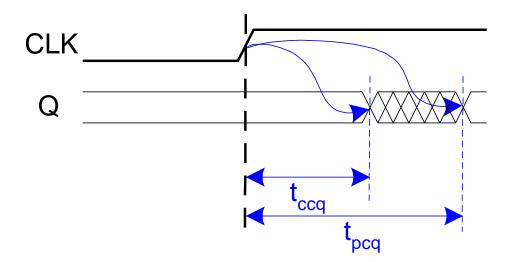

## **Output Timing Constraints**

- **Propagation delay:**  $t_{pcq}$  = time after clock edge that the output Q is guaranteed to be stable (i.e., to stop changing)

- Contamination delay:  $t_{ccq}$  = time after clock edge that Q might be unstable (i.e., start changing)

## **Dynamic Discipline**

- Synchronous sequential circuit inputs must be stable during aperture (setup and hold) time around clock edge

- Specifically, inputs must be stable:

- at least  $t_{\text{setup}}$  before the clock edge

- at least until  $t_{hold}$  after the clock edge

- Previously, static discipline:

- With logically valid inputs, every circuit element must produce logically valid outputs

## **Dynamic Discipline**

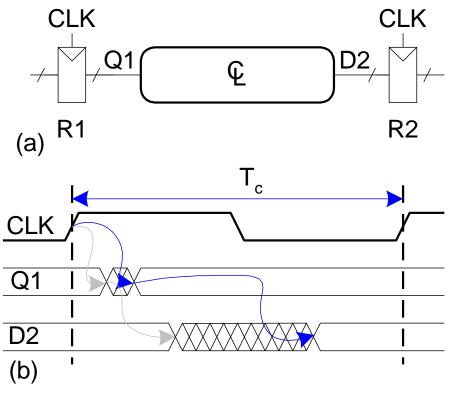

The delay between registers has a minimum and maximum delay, dependent on the delays of the circuit elements

ELSEVIER

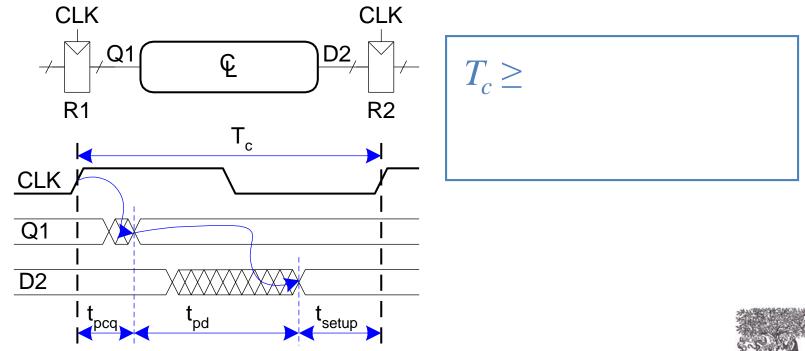

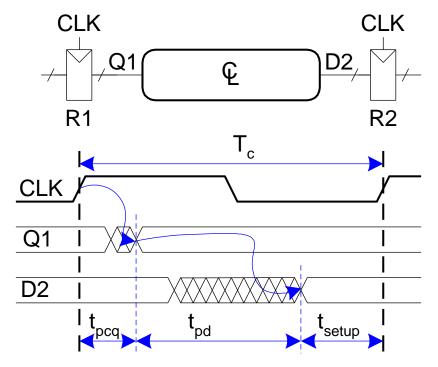

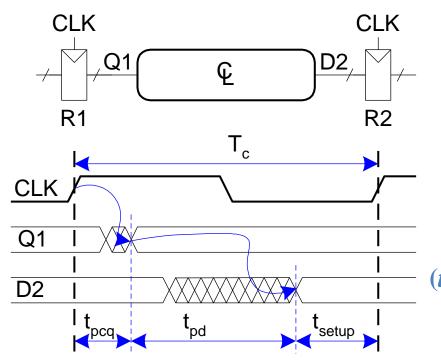

## Setup Time Constraint

- Depends on the maximum delay from register R1 through combinational logic to R2

- The input to register R2 must be stable at least t<sub>setup</sub> before clock edge

### Setup Time Constraint

- Depends on the maximum delay from register R1 through combinational logic to R2

- The input to register R2 must be stable at least t<sub>setup</sub> before clock edge

$T_c \ge t_{pcq} + t_{pd} + t_{setup}$  $t_{pd} \leq$

© Digital Design and Computer Architecture, 2<sup>nd</sup> Edition, 2012

### Setup Time Constraint

- Depends on the maximum delay from register R1 through combinational logic to R2

- The input to register R2 must be stable at least t<sub>setup</sub> before clock edge

$T_c \ge t_{pcq} + t_{pd} + t_{setup}$  $t_{pd} \leq T_c - (t_{pca} + t_{setup})$

$(t_{pcq} + t_{setup})$ : sequencing overhead

© Digital Design and Computer Architecture, 2<sup>nd</sup> Edition, 2012

Chapter 3 <74>

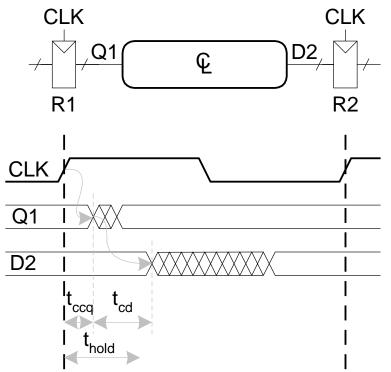

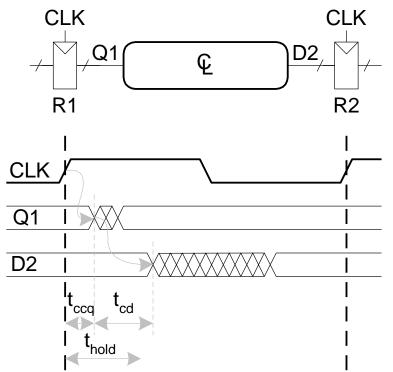

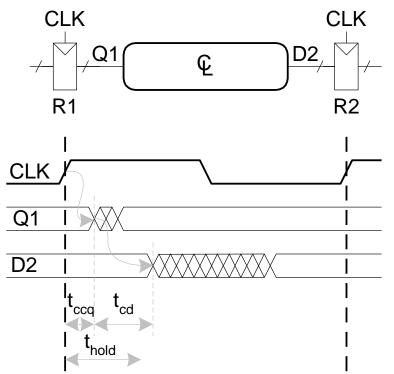

### Hold Time Constraint

- Depends on the minimum delay from register R1 through the combinational logic to R2

- The input to register R1 must be stable for at least  $t_{\rm hold}$  after the clock edge

### Hold Time Constraint

- Depends on the minimum delay from register R1 through the combinational logic to R2

- The input to register R1 must be stable for at least  $t_{\rm hold}$  after the clock edge

$t_{\text{hold}} < t_{ccq} + t_{cd}$  $t_{cd} >$

### Hold Time Constraint

- Depends on the minimum delay from register R1 through the combinational logic to R2

- The input to register R2 must be stable for at least  $t_{hold}$  after the clock edge

$t_{\text{hold}} < t_{ccq} + t_{cd}$  $t_{cd} > t_{hold} - t_{cca}$

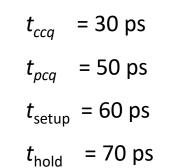

**Timing Characteristics**

$t_{ccq}$  = 30 ps

$t_{pcq}$  = 50 ps

$t_{setup} = 60 \text{ ps}$

$t_{\text{hold}}$  = 70 ps

$\begin{bmatrix} t_{pd} & = 35 \text{ ps} \\ t_{cd} & = 25 \text{ ps} \end{bmatrix}$

$t_{pd} =$  $t_{cd} =$

Setup time constraint:

$T_c \ge t_{pcq} + t_{pd} + t_{setup}$

$f_c =$

© Digital Design and Computer Architecture, 2<sup>nd</sup> Edition, 2012

#### Hold time constraint:

$$t_{\rm ccq} + t_{cd} > t_{\rm hold}$$

?

*t<sub>pd</sub>* = 3 x 35 ps = 105 ps

*t<sub>cd</sub>* = 25 ps

#### Setup time constraint:

$T_c \ge t_{pcq} + t_{pd} + t_{setup}$  $T_c \ge (50 + 105 + 60) \text{ ps} = 215 \text{ ps}$  $f_c = 1/T_c = 4.65 \text{ GHz}$

© Digital Design and Computer Architecture, 2<sup>nd</sup> Edition, 2012

### Timing Characteristics

$t_{ccq}$  = 30 ps

$$t_{pcq}$$

= 50 ps

$$t_{\text{setup}} = 60 \text{ ps}$$

$t_{\text{hold}}$  = 70 ps

$$\begin{bmatrix} t_{pd} & = 35 \text{ ps} \\ t_{cd} & = 25 \text{ ps} \end{bmatrix}$$

#### Hold time constraint:

$t_{ccq} + t_{cd} > t_{hold}$  ?

(30 + 25) ps > 70 ps ? No!

Chapter 3 <79>

Add buffers to the short paths:

### **Timing Characteristics**

$$\begin{bmatrix} \mathbf{t}_{pd} &= 35 \text{ ps} \\ \mathbf{t}_{cd} &= 25 \text{ ps} \end{bmatrix}$$

#### Hold time constraint:

$$t_{ccq} + t_{cd} > t_{hold}$$

?

Setup time constraint:

$t_{pd}$  =

$t_{cd} =$

$T_c \ge$

$f_c =$

Add buffers to the short paths:

*t<sub>pd</sub>* = 3 x 35 ps = 105 ps

$t_{cd}$  = 2 x 25 ps = 50 ps

#### Setup time constraint:

$T_c \ge t_{pcq} + t_{pd} + t_{setup}$  $T_c \ge (50 + 105 + 60) \text{ ps} = 215 \text{ ps}$  $f_c = 1/T_c = 4.65 \text{ GHz}$

© Digital Design and Computer Architecture, 2<sup>nd</sup> Edition, 2012

### **Timing Characteristics**

- $t_{ccq}$  = 30 ps  $t_{pcq}$  = 50 ps  $t_{setup}$  = 60 ps

- $t_{\text{hold}}$  = 70 ps

$$\begin{bmatrix} t_{pd} & = 35 \text{ ps} \\ t_{cd} & = 25 \text{ ps} \end{bmatrix}$$

#### Hold time constraint:

$$t_{ccq} + t_{cd} > t_{hold}$$

?

(30 + 50) ps > 70 ps ? Yes!

# Parallelism

- Two types of parallelism:

- Spatial parallelism

- duplicate hardware performs multiple tasks at once

- Temporal parallelism

- task is broken into multiple stages

- also called pipelining

- for example, an assembly line

# **Parallelism Definitions**

- **Token:** Group of inputs processed to produce group of outputs

- Latency: Time for one token to pass from start to end

- **Throughput:** Number of tokens produced per unit time

### **Parallelism increases throughput**

- Ben Bitdiddle bakes cookies to celebrate traffic light controller installation

- 5 minutes to roll cookies

- 15 minutes to bake

- What is the latency and throughput without parallelism?

- Ben Bitdiddle bakes cookies to celebrate traffic light controller installation

- 5 minutes to roll cookies

- 15 minutes to bake

- What is the latency and throughput without parallelism?

Latency = 5 + 15 = 20 minutes = 1/3 hour Throughput = 1 tray/ 1/3 hour = 3 trays/hour

- What is the latency and throughput if Ben uses parallelism?

- Spatial parallelism: Ben asks Allysa P. Hacker to help, using her own oven

- Temporal parallelism:

- two stages: rolling and baking

- He uses two trays

- While first batch is baking, he rolls the second batch, etc.

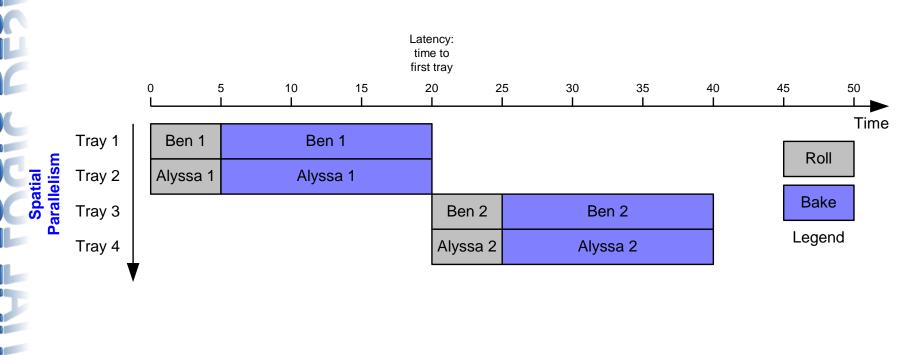

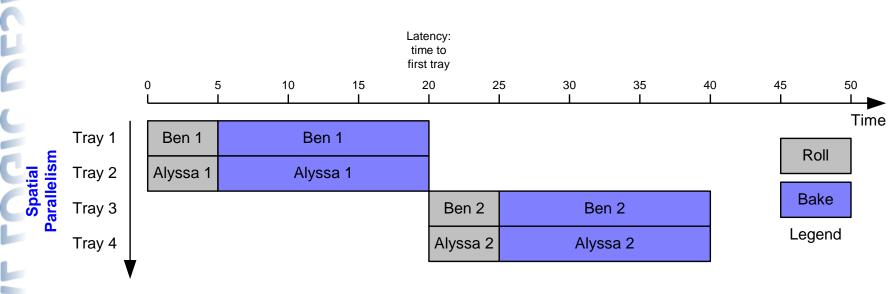

### **Spatial Parallelism**

Latency = ? Throughput = ?

© Digital Design and Computer Architecture, 2<sup>nd</sup> Edition, 2012

Chapter 3 <87>

### **Spatial Parallelism**

Latency = 5 + 15 = 20 minutes = 1/3 hour Throughput = 2 trays/ 1/3 hour = 6 trays/hour

© Digital Design and Computer Architecture, 2<sup>nd</sup> Edition, 2012

Chapter 3 <88>

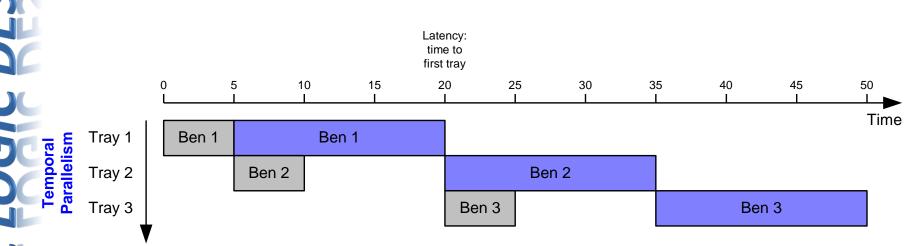

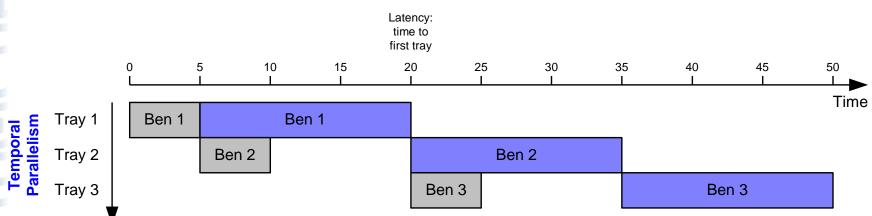

### **Temporal Parallelism**

Latency = ? Throughput = ?

© Digital Design and Computer Architecture, 2<sup>nd</sup> Edition, 2012

Chapter 3 <89>

### **Temporal Parallelism**

Latency = 5 + 15 = 20 minutes = 1/3 hour

$\rightarrow$  true latency = 30 minutes (with 10 minutes idle) **Throughput** = 1 trays/ 1/4 hour = 4 trays/hour

Using both spatial and temporal techniques, the throughput would be **8 trays/hour** © Digital Design and Computer Architecture, 2<sup>nd</sup> Edition, 2012 Chapter 3 <90>

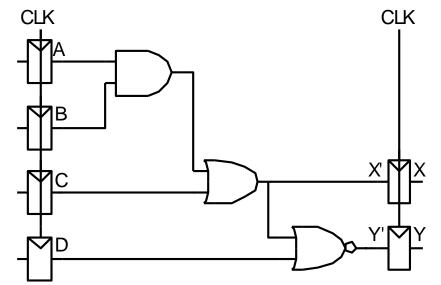

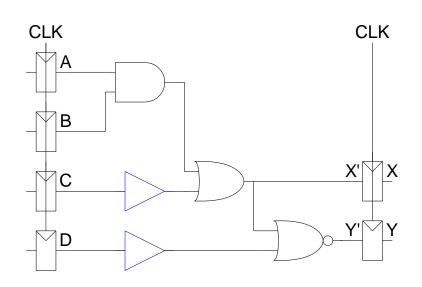

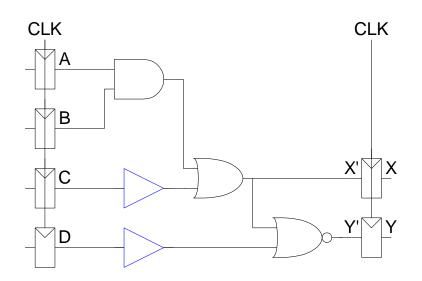

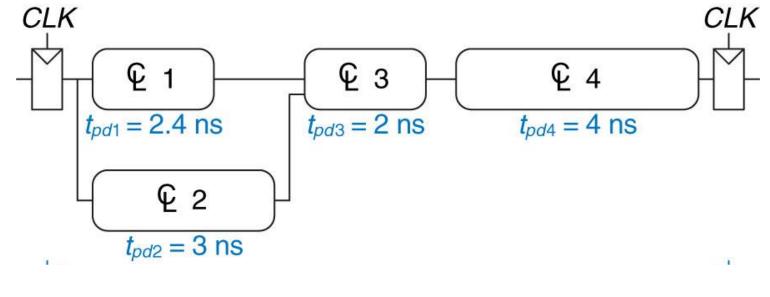

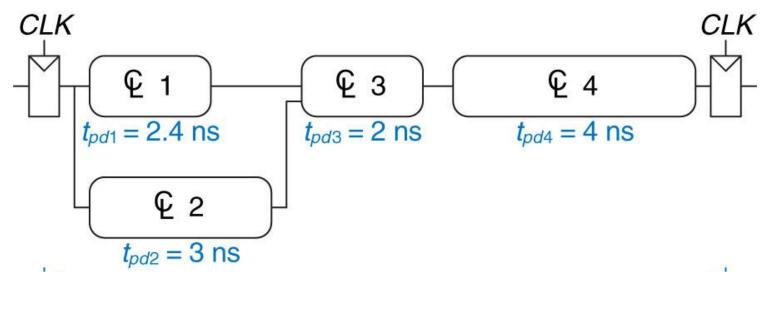

- Circuit with no parallelism

- Registers have:

- Propagation clock-to-Q = 0.3 ns

- Setup time = 0.2 ns

- Circuit with no parallelism

- Find critical path

- Compute minimum cycle time, latency, and throughput

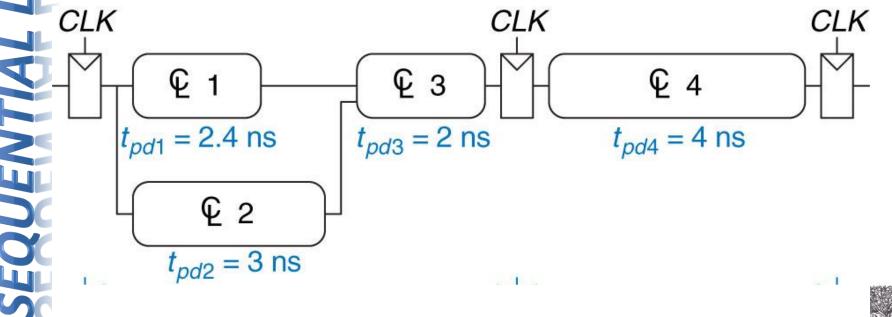

- Circuit with parallelism: 2 stages

- Find critical path

- Compute minimum cycle time, latency, and throughput

© Digital Design and Computer Architecture, 2<sup>nd</sup> Edition, 2012

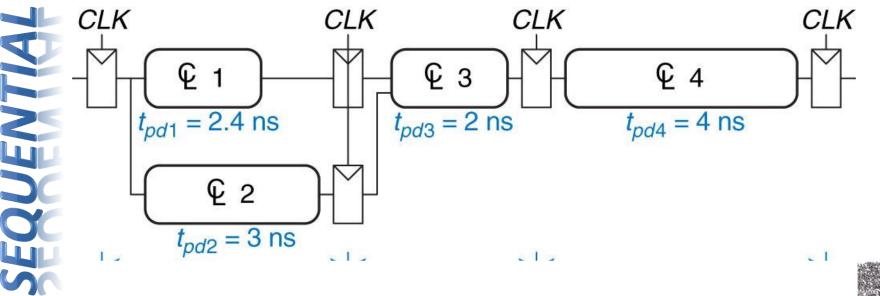

- Circuit with parallelism: 3 stages

- Find critical path

- Compute minimum cycle time, latency, and throughput

© Digital Design and Computer Architecture, 2<sup>nd</sup> Edition, 2012