# CPE300: Digital System Architecture and Design

Fall 2011 MW 17:30-18:45 CBC C316

1-Bus Architecture and Datapath 10262011

http://www.egr.unlv.edu/~b1morris/cpe300/

#### Outline

- 1-Bus Microarchitecture and Datapath Review

- 1-Bus Logic Design

- Control Unit

# **Register Transfer Descriptions**

- Abstract RTN

- Defines "what" not the "how" (Chapter 2)

- Overall effect of instructions on programmer-visible registers

- Implementation independent

- Registers and operations

- Concrete RTN

- Detailed register transfer steps in datapath to produce overall effect

- Dependent on implementation details

- Steps correspond to processor clock pulses

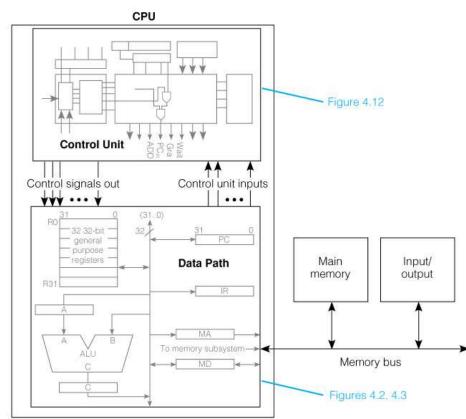

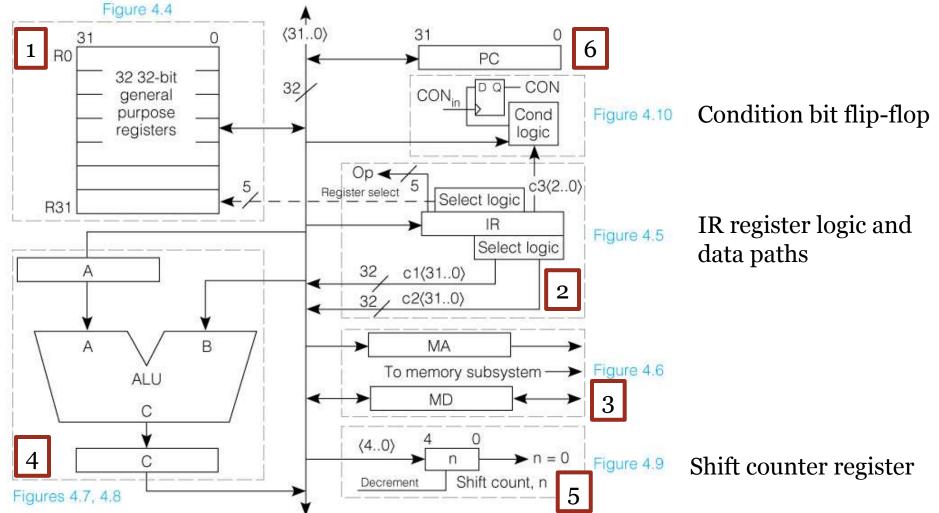

#### **1-Bus SRC Microarchitecture**

- 5 classic components of computer

- Memory, Input, Output

- CPU Control and Datapath

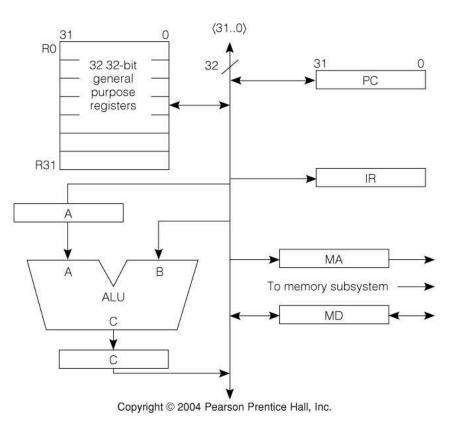

# Microarchitecture Constraints

- One bus connecting registers

- Only single register transfer at a time

- Memory address must be copied into memory address (MA) register by CPU

- Memory data written from or read into memory data (MD) register

- ALU operation

- First operand always registered in A

- Second operand always comes from bus

- Result registered in C

- Information into IR and MA only from bus

- Decoder (not shown) interprets contents of IR

- MA supplies address to memory not CPU bus

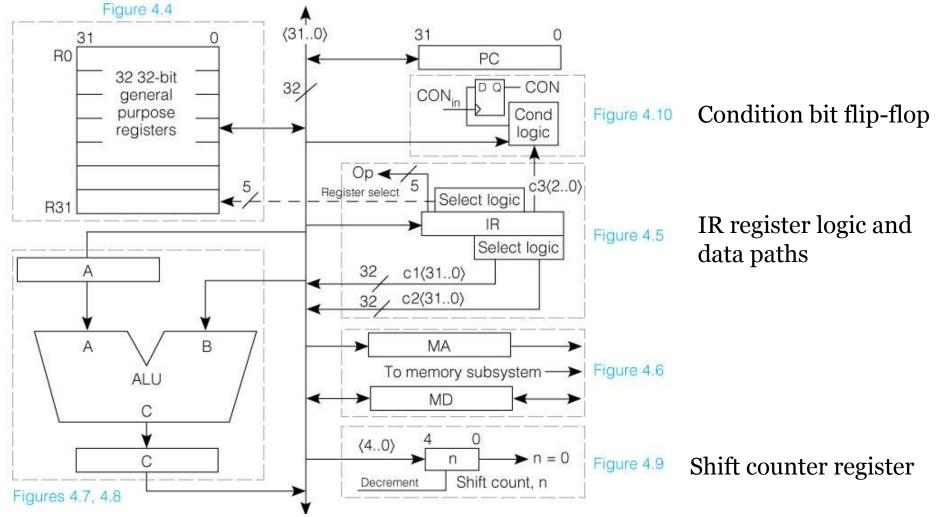

#### More Complete View of 1-Bus SRC Design

• Concrete RTN adds detail to the datapath

#### RTN for ADD Instruction

- Develop steps to execute instruction

- Abstract RTN

- Instruction\_execution := (...

- add(:=op=12)  $\rightarrow$  R[ra]  $\leftarrow$  R[rb]+R[rc]:

- ...);

- Concrete RTN

- 3 concrete RT (T3, T4, T5)

- 2 RT in To

- 6 total clock cycles

| Step | RTN                                      |          |

|------|------------------------------------------|----------|

| ТО   | MA $\leftarrow$ PC: C $\leftarrow$ PC+4; | -c       |

| Т1   | MD←M[MA]: PC←C                           | fetch    |

| Т2   | IR←MD                                    |          |

| Т3   | A←R[rb]                                  | lon      |

| Т4   | C←A+R[rc];                               | xecutior |

| Т5   | R[ra] <b>←</b> C                         | ехе      |

#### RTN for ADD Instruction

- Develop steps to execute instruction

- Abstract RTN

- Instruction\_execution := (...

- add(:=op=12)  $\rightarrow$  R[ra]  $\leftarrow$  R[rb]+R[rc]:

- ...);

- Concrete RTN

- 3 concrete RT (T3, T4, T5)

- 2 RT in To

- 6 total clock cycles

| Step | RTN                                      |          |

|------|------------------------------------------|----------|

| ТО   | MA $\leftarrow$ PC: C $\leftarrow$ PC+4; |          |

| Т1   | MD←M[MA]: PC←C                           | fetch    |

| Т2   | IR←MD                                    |          |

| ТЗ   | A←R[rb]                                  | lon      |

| Т4   | C←A+R[rc];                               | xecution |

| Т5   | R[ra] <b>←</b> C                         | exe      |

### RTN for Load/Store Instruction

#### Abstract RTN

- $ld(:=op=1) \rightarrow R[ra] \leftarrow M[disp]:$

- st(:=op=3)  $\rightarrow$  M[disp]  $\leftarrow$  R[ra]:

- disp<31..0>:=((rb=0)→c2<16..0> {sign-extend}:

$(rb\neq 0) \rightarrow R[rb]+c2<16...0> \{sign-ext, 2's comp\}$

#### Concrete RTN

| Step  | RTN 1d                   | RTN st                 |

|-------|--------------------------|------------------------|

| т0-т2 | Instruction Fetch        |                        |

| Т3    | A←(rb=0→0: rb≠0→R        | [rb]);                 |

| Т4    | C←A+(16@IR<16>#IR<150>); |                        |

| Т5    | $MA \leftarrow C;$       |                        |

| Т6    | $MD \leftarrow M[MA];$   | MD <b>←</b> R[ra]      |

| т7    | R[ra]←MD;                | $M[MA] \leftarrow MD;$ |

#### T<sub>3</sub>, T<sub>4</sub> are effective address arithmetic calculation

#### Notes for Load/Store RTN

- To-T2 are same as for add (all instructions)

- T3-T5 are same for ld and st calculate disp

- Need way to use 0 for R[rb] when rb=0

- 15-bit sign extension of IR<16..0> is needed

- Memory read into MD at T6 of ld

- Write of MD into memory at T7 of st

# **RTN for Conditional Branch**

#### Abstract RTN

- $br(:=op=8) \rightarrow (cond \rightarrow PC \leftarrow R[rb]):$

- cond:=(

- c3<2..0>=0→0:

- c3<2..0>=1→1:

- c3<2..0>=2→R[rc]=0:

- c3<2..0>=3→R[rc]≠0:

- c3<2..0>=4→R[rc]<31>=0:

- c3<2..0>=5→R[rc]<31>=1 ):

#### Concrete RTN

| alv | vays     |    |          |    |      |

|-----|----------|----|----------|----|------|

| if  | register | is | zero     |    |      |

| if  | register | is | nonzero  |    |      |

| if  | register | is | positive | or | zero |

| if  | register | is | negative |    |      |

;never

| Step  | RTN                                    |

|-------|----------------------------------------|

| T0-T2 | Instruction Fetch                      |

| Т3    | CON←cond(R[rc]);                       |

| Т4    | $CON \rightarrow PC \leftarrow R[rb];$ |

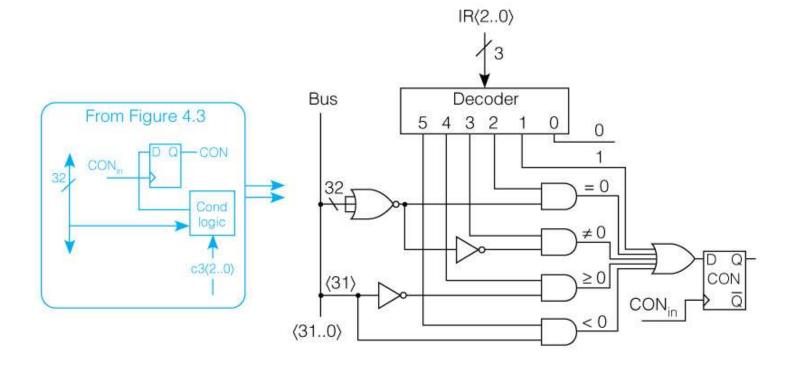

CON is 1-bit register that is set based on condition logic: the contents of c<2..0> and R[rc]

### Notes on Conditional Branch RTN

- c3<2..0> are just 3 low order bits of IR

- cond() is evaluated by combinational logic

circuit having inputs R[rc] and c3<2..0>

- One bit CON register is not accessible to the programmer

- Holds intermediate output of combinational logic for the condition

- If branch succeeds

- PC is replaced by contents of a general register

# RTN for SRC Shift Right

#### Abstract RTN

shr(:=op=26) → R[ra] <31..0> ← (n@0) #R[rb] <31..n>:

• n:=((c3<4..0>=0)→R[rc]<4..0>: (c3<4..0>≠0)→c3<4..0>): ;shift count in reg. ;shift cnt const. field

#### Concrete RTN

| Step  | RTN                                             |

|-------|-------------------------------------------------|

| т0-т2 | Instruction Fetch                               |

| Т3    | n <b>←</b> IR<40>                               |

| Т4    | $(n=0) \rightarrow (n \leftarrow R[rc] < 40>);$ |

| Т5    | $C \leftarrow R[rb]$                            |

| Тб    | Shr(:=n≠0→(C<310>←0#C<311>: n←n-1; Shr));       |

| т7    | R[ra] ←C                                        |

T6 is repeated n times

#### Notes on Shift RTN

- Abstract RTN defines n with :=

- Concrete RTN has n as a physical register

- n is not only the shift count but used as a counter in step T6

- T6 is repeated n times through recursive Shr call

- Will require more complicated control, described later

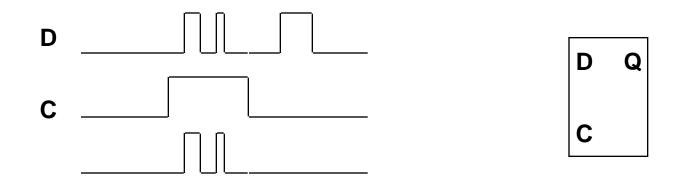

# Datapath/Control Unit Separation

- Interface between datapath and control consists of gate and strobe signals

- Gate selects one of several values to apply to a common point (e.g. bus)

- Strobe changes the contents of a register (flipflops) to match new inputs

- Type of flip-flop used in a register has significant impact on control and limited impact on datapath

- Latch simpler hardware but more complex timing

- Edge triggered simpler timing but approximately 2x hardware

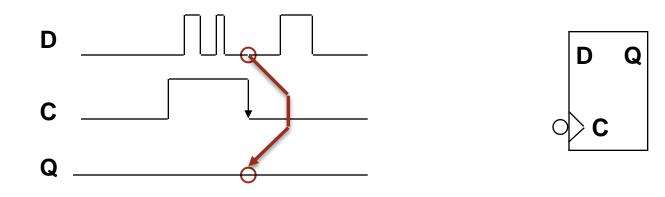

### Latch/Edge-Triggered Operation

Latch output follows input while strobe is high

• Edge-triggering samples input at the edge time

#### More Complete View of 1-Bus SRC Design

Add control signals and gate-level logic

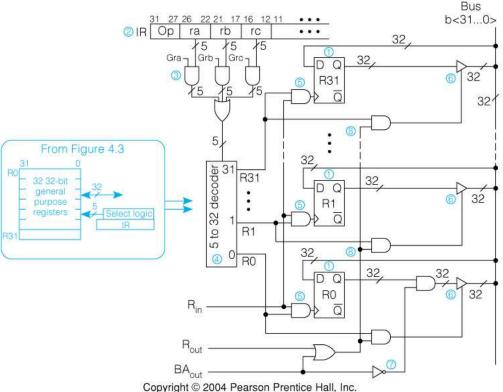

# **Register File and Control Signals**

- Register selection

- IR decode of register fields

- Grx signal to gate register rx by decoder

- R<sub>out</sub> gates selected register onto the bus

- R<sub>in</sub> strobes selected register from the bus

- Base address out BAout gates zero signal when R[0] is selected

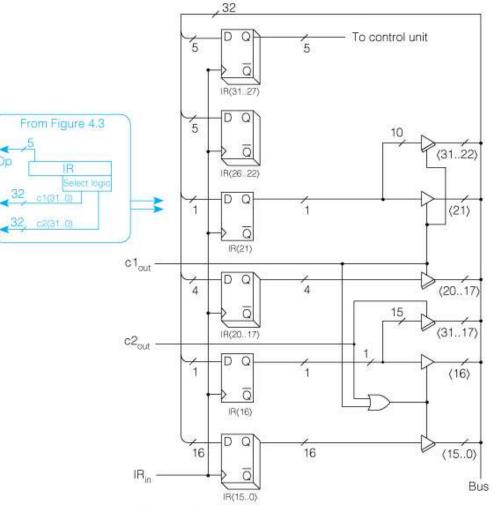

# Extracting Constants/op from IR

4 Op

- 3D blocks distinguish multi-bi elements

- **Register flip-flops**

- Tri-state bus drivers

- Sign bits fanned out from one to several bits and gated onto bus

- IR<21> is sign bit of c1 and must be sign extended

- IR<16> is sign bit of c2 and must be sign extended

Copyright © 2004 Pearson Prentice Hall, Inc.

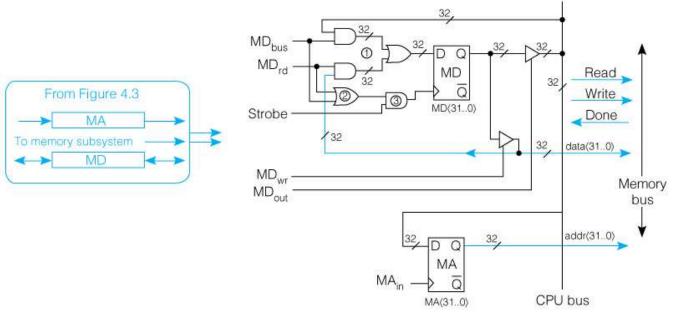

### Memory Interface

- MD is loaded from memory bus or from CPU bus

- MD can drive memory bus or CPU bus

- MA only gets address from CPU processor bus

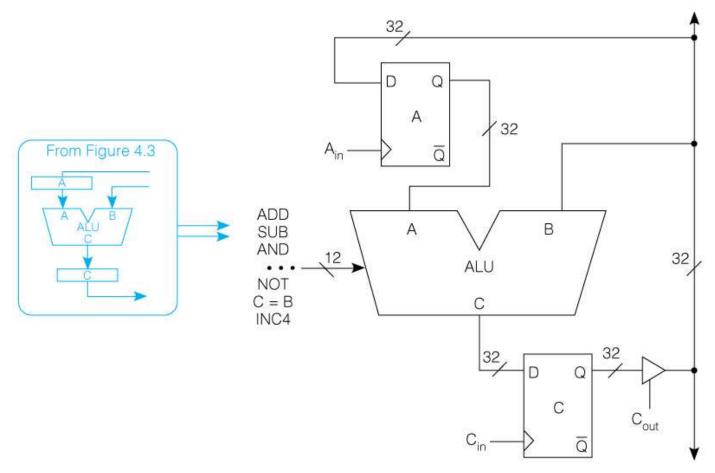

### ALU and Associated Registers

Add control lines to select ALU function

INC4 for hardware supported PC increment

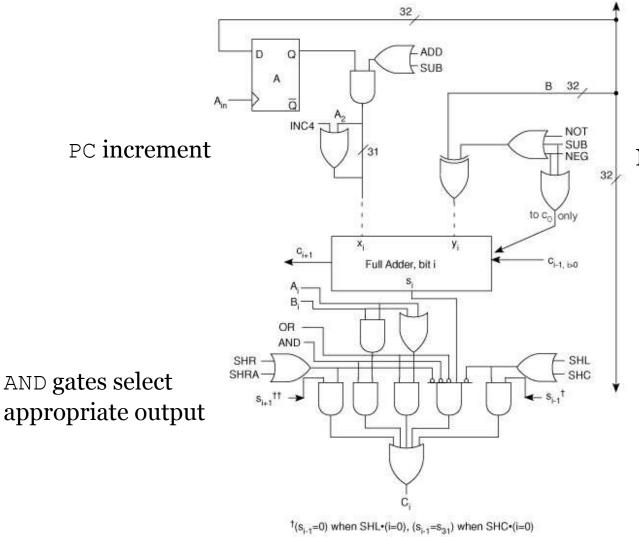

# 1-Bit ALU Logic-Level Design

Negative numbers in B

$^{++}(s_{i+1}=0)$  when SHR•(i=31),  $(s_{i+1}=s_{31})$  when SHRA•(i=31)

# **Control Sequences**

- Register transfers are the concrete RTN

- Control sequence are the control signals that cause the RT

| Step | Concrete RTN                             | <b>Control Sequence</b>                                      |

|------|------------------------------------------|--------------------------------------------------------------|

| TO   | MA $\leftarrow$ PC: C $\leftarrow$ PC+4; | PC <sub>out</sub> , MA <sub>in</sub> , Inc4, C <sub>in</sub> |

| Т1   | MD←M[MA]: PC←C                           | Read, C <sub>out</sub> , PC <sub>in</sub> , Wait             |

| Т2   | IR <b>←</b> MD                           | MD <sub>out</sub> , IR <sub>in</sub>                         |

| ТЗ   | instruction_execution                    |                                                              |

Wait prevents control sequence from advancing to step T2 until memory asserts Done

#### Control Steps, Control Signals, and Timing

- Order control signals are written is irrelevant for a given time step

- Step To:

- (Inc4, C<sub>in</sub>, PC<sub>out</sub>, MA<sub>in</sub>) = (PC<sub>out</sub>, MA<sub>in</sub>, Inc4, C<sub>in</sub>)

- Timing distinction is made between gates and strobes

- Gates early, strobes late in clock cycle

- Memory read should start as early as possible to reduce wait time

- MA must have correct value before being used for a read

#### Control for ADD Instruction

• add(:=op=12) $\rightarrow$ R[ra] $\leftarrow$ R[rb]+R[rc]:

| Step | Concrete RTN                             | <b>Control Sequence</b>                                      |

|------|------------------------------------------|--------------------------------------------------------------|

| ТО   | MA $\leftarrow$ PC: C $\leftarrow$ PC+4; | PC <sub>out</sub> , MA <sub>in</sub> , Inc4, C <sub>in</sub> |

| T1   | MD←M[MA]: PC←C                           | Read, C <sub>out</sub> , PC <sub>in</sub> , Wait             |

| Т2   | IR <b>←</b> MD                           | MD <sub>out</sub> , IR <sub>in</sub>                         |

| Т3   | A←R[rb]                                  | Grb, R <sub>out</sub> , A <sub>in</sub>                      |

| Т4   | C←A+R[rc];                               | Grc, R <sub>out</sub> , ADD, C <sub>in</sub>                 |

| Т5   | R[ra] <b>←</b> C                         | C <sub>out</sub> , Gra, R <sub>in</sub> , End                |

- Grx used to gate correct 5-bit register select code

- End signals the control to start over at step To

#### RTN for ADDI Instruction

• addi(:=op=13)→R[ra]←R[rb]+c2<16..0> {two's

complement, sign-extend}:

| Step | Concrete RTN                             | Control Sequence                                             |

|------|------------------------------------------|--------------------------------------------------------------|

| ТО   | MA $\leftarrow$ PC: C $\leftarrow$ PC+4; | PC <sub>out</sub> , MA <sub>in</sub> , Inc4, C <sub>in</sub> |

| Τ1   | MD←M[MA]: PC←C                           | Read, C <sub>out</sub> , PC <sub>in</sub> , Wait             |

| Т2   | IR←MD                                    | MD <sub>out</sub> , IR <sub>in</sub>                         |

| Т3   | A←R[rb]                                  | Grb, R <sub>out</sub> , A <sub>in</sub>                      |

| Т4   | $C \leftarrow A+c2 \{ sign-extend \};$   | c2 <sub>out</sub> , ADD, C <sub>in</sub>                     |

| Т5   | R[ra] <b>←</b> C                         | C <sub>out</sub> , Gra, R <sub>in</sub> , End                |

C2<sub>out</sub> signal sign extends IR<16..0> and gates it to the bus

#### RTN for st Instruction

• st(:=op=3)  $\rightarrow$  M[disp]  $\leftarrow$  R[ra]:

• disp<31..0>:=((rb=0)→c2<16..0> {sign-extend}:

$(rb\neq 0) \rightarrow R[rb]+c2<16..0> \{sign-ext, 2's comp\}$

| Step  | Concrete RTN                                                     | <b>Control Sequence</b>                          |

|-------|------------------------------------------------------------------|--------------------------------------------------|

| т0-т2 | instruction_fetch                                                |                                                  |

| Т3    | $A \leftarrow (rb=0 \rightarrow 0: rb\neq 0 \rightarrow R[rb]);$ | Grb, BA <sub>out</sub> , A <sub>in</sub>         |

| Т4    | C←A+(16@IR<16>#IR<150>);                                         | c2 <sub>out</sub> , ADD, C <sub>in</sub>         |

| Т5    | MA <b>←</b> C;                                                   | C <sub>out</sub> , MA <sub>in</sub>              |

| Т6    | MD←R[ra]                                                         | Gra, R <sub>out</sub> , MD <sub>in</sub> , Write |

| т7    | M[MA] ← MD;                                                      | Wait, End                                        |

• Notice the use of  $BA_{out}$  in step T3 not  $R_{out}$  as done in addi

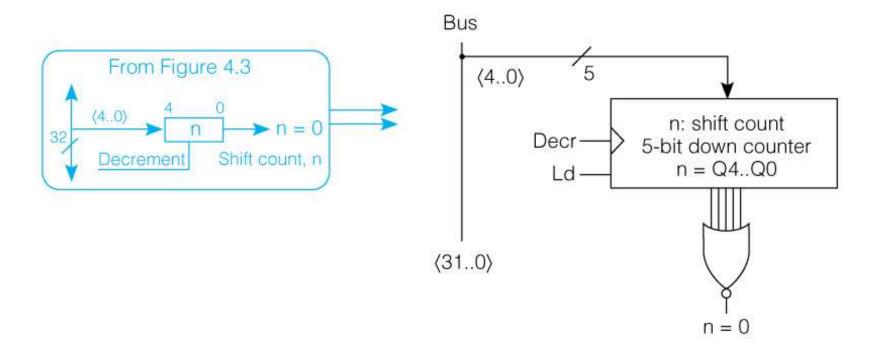

#### Shift Counter

- Concrete RTN for shr relies upon a 5-bit register to hold the shift count

- Must load, decrement, and have a way to test if the contents equal o

#### **Control for Shift Instruction**

- shr(:=op=26)→R[ra]<31..0>←(n@0)#R[rb]<31..n>:

- n:=((c3<4..0>=0)→R[rc]<4..0>: ;shift count in reg. (c3<4..0>≠0)→c3<4..0>): ;count const. field

| Step  | Concrete RTN                                                       | Control Sequence                                               |

|-------|--------------------------------------------------------------------|----------------------------------------------------------------|

| т0-т2 | Instruction Fetch                                                  |                                                                |

| Т3    | n <b>←</b> IR<40>                                                  | clout, Ld                                                      |

| Т4    | $(n=0) \rightarrow (n \leftarrow R[rc] < 40>);$                    | $n=0 \rightarrow (Grc, R_{out}, Ld)$                           |

| Т5    | $C \leftarrow R[rb]$                                               | Grb, R <sub>out</sub> , C=B, C <sub>in</sub>                   |

| Тб    | <pre>Shr(:=n≠0→  (C&lt;310&gt;←0#C&lt;311&gt;: n←n-1; Shr));</pre> | n≠0→(C <sub>out</sub> , SHR, C <sub>in</sub> , Decr,<br>Goto6) |

| т7    | R[ra] ←C                                                           | C <sub>out</sub> , Gra, R <sub>in</sub> , End                  |

- Conditional control signals and repeating control are new concepts

- Goto6 repeats step T6 but must be carefully timed for the looping

# Branching

- Branch conditions dependent on cond field an a register value (not flag or flag register)

- cond:=(

- c3<2..0>=0→0:

- c3<2..0>=1→1:

- c3<2..0>=2→R[rc]=0:

- c3<2..0>=3→R[rc]≠0:

- c3<2..0>=4→R[rc]<31>=0:

- c3<2..0>=5→R[rc]<31>=1 ): ;if register is negative

- ;never

;always

;if register is zero

;if register is nonzero

;if register is positive or zero

;if register is negative

#### Logic expression for condition

```

ouble cond = (c3<2..0>=1) ∨ (c3<2..0>=2) ∧ (R[rc]=0) ∨

(c3<2..0>=3) ∧ ¬(R[rc]=0) ∨ (c3<2..0>=4) ∧ ¬R[rc]<31>

∨ (c3<2..0>=5) ∧ R[rc]<31>

```

#### **Conditional Value Computation**

• NOR gate does test of R[rc]=0 on bus

### **Control for Branch Instruction**

• br(:=op=8)  $\rightarrow$  (cond $\rightarrow$  PC $\leftarrow$  R[rb]):

| Step  | Concrete RTN                           | Control Sequence                                 |

|-------|----------------------------------------|--------------------------------------------------|

| т0-т2 | Instruction Fetch                      |                                                  |

| Т3    | CON←cond(R[rc]);                       | Grc, R <sub>out</sub> , CON <sub>in</sub>        |

| Т4    | $CON \rightarrow PC \leftarrow R[rb];$ | Grb, $R_{out}$ , $CON \rightarrow PC_{in}$ , End |

- Condition logic always connected to CON

- R[rc] only needs to be placed on bus in T3

- Only PC<sub>in</sub> is conditional in T4 since gating R[rb] to bus makes no difference if it is not used

# Summary of Design Process

- Informal description ⇒ formal RTN description ⇒ block diagram arch. ⇒ concrete RTN steps ⇒ hardware design of blocks ⇒ control sequences ⇒ control unit and timing

- At each level, more decisions must be made

- These decisions refine the design

- Also place requirements on hardware still to be designed

- The nice one way process above has circularity

- Decisions at later stages cause changes in earlier ones

- Happens less in a text than in reality because

- Can be fixed on re-reading

- Confusing to first time student

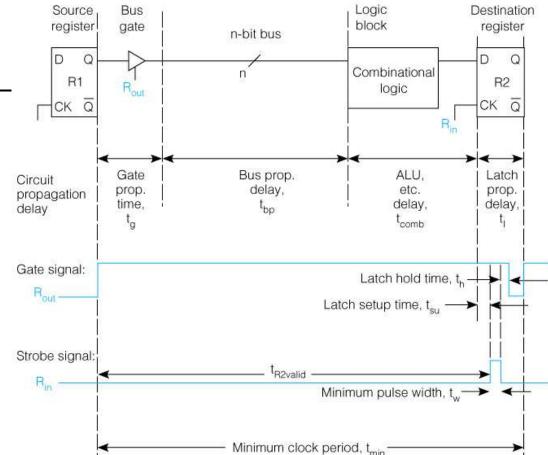

# **Clocking the Datapath**

- Register transfers result from information processing

- Register transfer timing register to register

- Level sensitive latch flipflops in example

- t<sub>R2valid</sub> is the period from begin of gate signal till inputs at R2 are valid

- t<sub>comb</sub> is delay through combinational logic, such as ALU or cond logic

34

# Signal Timing on the Datapath

- Several delays occur in getting data from R1 to R2

- Gate delay through the 3-state bus driver—t<sub>g</sub>

- Worst case propagation delay on bus—t<sub>bp</sub>

- Delay through any logic, such as ALU—t<sub>comb</sub>

- Set up time for data to affect state of R2-t<sub>su</sub>

- Data can be strobed into R2 after this time

$t_{R2valid} = t_g + t_{bp} + t_{comb} + t_{su}$

- Diagram shows strobe signal in the form for a latch. It must be high for a minimum time—t<sub>w</sub>

- There is a hold time, t<sub>h</sub>, for data after strobe ends

#### Signal Timing and Minimum Clock Cycle

• A total latch propagation delay is the sum

$T_l = t_{su} + t_w + t_h$

- All above times are specified for latch

- t<sub>h</sub> may be very small or zero

- The minimum clock period is determined by finding longest path from flip-flop output to flipflop input

- This is usually a path through the ALU

- Conditional signals add a little gate delay

- Minimum clock period is

$$\mathbf{t}_{\min} = \mathbf{t}_{g} + \mathbf{t}_{bp} + \mathbf{t}_{comb} + \mathbf{t}_{l}$$

# Consequences of Flip-Flop Type

- Flip-flop types (Appendix A.12)

- Level-triggered (latch) state can change while clock is high

- Edge-triggered state changes only on a clock transition (highto-low or low-to-high)

- Master-slave breaks feedback from output/input of register allowing on a single state change per clock cycle

- During the high part of a strobe a latch changes its output

- If this output can affect its input, an error can occur (feeback)

- This can influence even the kind of concrete RTs that can be written for a data path

- If the C register is implemented with latches, then  $C \leftarrow C + MD$ ; is not legal

- If the C register is implemented with master-slave or edge triggered flip-flops, it is OK

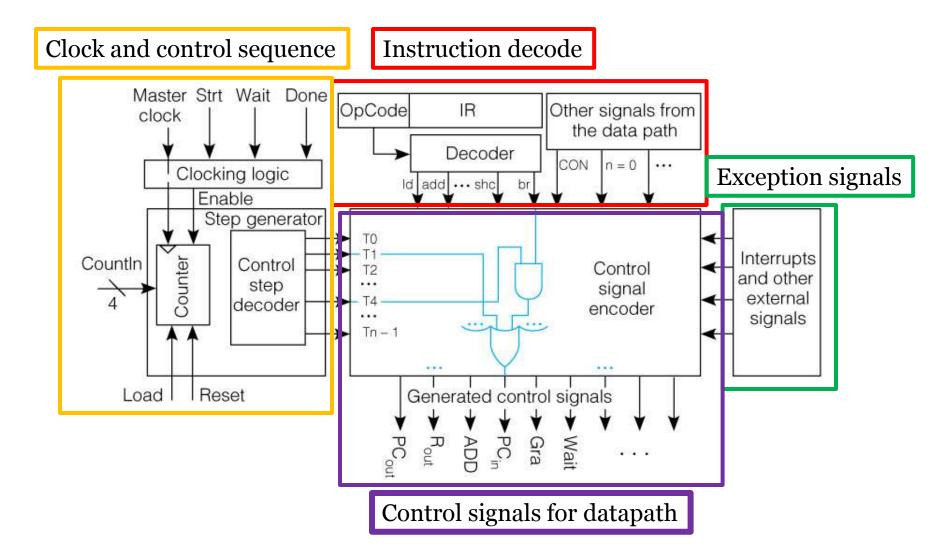

# The Control Unit

- Brain of a machine

- Datapath implementation led to control sequences to implement instructions

- Control unit will generate the control sequences

- Logic to enable control signal

- Timing of signals

- The control unit's job is to generate the control signals in the proper sequence

- Things the control signals depend on

- The time step Ti

- The instruction op code (for steps other than To, T1, T2)

- Some few datapath signals like CON, n=0, etc.

- Some external signals: reset, interrupt, etc. (to be covered)

- The components of the control unit are: a time state generator, instruction decoder, and combinational logic to generate control signals

#### **Detailed Control Unit**

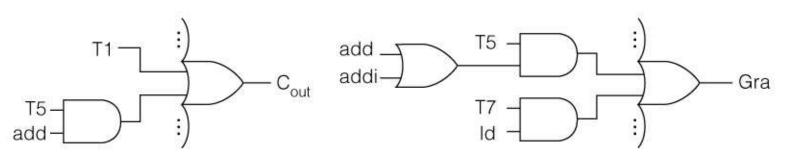

# Control Signal Encoder Logic

- Write equation describing control signal

- Find all occurrences of control signal in entire set of control sequences

- Equation implemented by digital logic gates

| Step | Fetch Control Sequence                                       | Step | ADD Control Sequence                          | Step | ADDI Control Sequence                         |

|------|--------------------------------------------------------------|------|-----------------------------------------------|------|-----------------------------------------------|

| ТO   | PC <sub>out</sub> , MA <sub>in</sub> , Inc4, C <sub>in</sub> | ТЗ   | Grb, R <sub>out</sub> , A <sub>in</sub>       | ТЗ   | Grb, R <sub>out</sub> , A <sub>in</sub>       |

| Τ1   | Read, C <sub>out</sub> , PC <sub>in</sub> , Wait             | Т4   | Grc, R <sub>out</sub> , ADD, C <sub>in</sub>  | Т4   | c2 <sub>out</sub> , ADD, C <sub>in</sub>      |

| Т2   | MD <sub>out</sub> , IR <sub>in</sub>                         | Т5   | C <sub>out</sub> , Gra, R <sub>in</sub> , End | Т5   | C <sub>out</sub> , Gra, R <sub>in</sub> , End |

| Step | SHR Control Sequence                                                      | Step | ST Control Sequence                              | Step | <b>BR Control Sequence</b>                |

|------|---------------------------------------------------------------------------|------|--------------------------------------------------|------|-------------------------------------------|

| Т3   | clout, Ld                                                                 | Т3   | Grb, BA <sub>out</sub> , A <sub>in</sub>         | Т3   | Grc, R <sub>out</sub> , CON <sub>in</sub> |

| Т4   | $n=0 \rightarrow (Grc, R_{out}, Ld)$                                      | Т4   | c2 <sub>out</sub> , ADD, C <sub>in</sub>         | Τ4   | Grb, R <sub>out</sub> ,                   |

| Т5   | Grb, R <sub>out</sub> , C=B, C <sub>in</sub>                              | Т5   | C <sub>out</sub> , MA <sub>in</sub>              |      | $CON \rightarrow PC_{in}$ , End           |

| Т6   | n≠0 $\rightarrow$ (C <sub>out</sub> , SHR, C <sub>in</sub> , Decr, Goto6) | Тб   | Gra, R <sub>out</sub> , MD <sub>in</sub> , Write |      |                                           |

| т7   | C <sub>out</sub> , Gra, R <sub>in</sub> , End                             | т7   | Wait, End                                        |      |                                           |

### **Control Signal Examples**

| Step | Fetch Control Sequence                                       | Step | ADD Control Sequence                          | Step | ADDI Control Sequence                         |

|------|--------------------------------------------------------------|------|-----------------------------------------------|------|-----------------------------------------------|

| ΤO   | PC <sub>out</sub> , MA <sub>in</sub> , Inc4, C <sub>in</sub> | ΤЗ   | Grb, R <sub>out</sub> , A <sub>in</sub>       | T3   | Grb, R <sub>out</sub> , A <sub>in</sub>       |

| Τ1   | Read, C <sub>out</sub> , PC <sub>in</sub> , Wait             | Т4   | Grc, R <sub>out</sub> , ADD, C <sub>in</sub>  | Τ4   | c2 <sub>out</sub> , ADD, C <sub>in</sub>      |

| Т2   | MD <sub>out</sub> , IR <sub>in</sub>                         | т5   | C <sub>out</sub> , Gra, R <sub>in</sub> , End | т5   | C <sub>out</sub> , Gra, R <sub>in</sub> , End |

| Step | SHR Control Sequence                          | Step | ST Control Sequence                              | Step | BR Control Sequence                       |

|------|-----------------------------------------------|------|--------------------------------------------------|------|-------------------------------------------|

| Т3   | clout, Ld                                     | Т3   | Grb, BA <sub>out</sub> , A <sub>in</sub>         | Т3   | Grc, R <sub>out</sub> , CON <sub>in</sub> |

| Τ4   | $n=0 \rightarrow (Grc, R_{out}, Ld)$          | Т4   | c2 <sub>out</sub> , ADD, C <sub>in</sub>         | Т4   | Grb, R <sub>out</sub> ,                   |

| Т5   | Grb, R <sub>out</sub> , C=B, C <sub>in</sub>  | Т5   | C <sub>out</sub> , MA <sub>in</sub>              |      | $CON \rightarrow PC_{in}$ , End           |

| Т6   | $n≠0→(C_{out}, SHR, C_{in}, Decr, Goto6)$     | Тб   | Gra, R <sub>out</sub> , MD <sub>in</sub> , Write |      |                                           |

| т7   | C <sub>out</sub> , Gra, R <sub>in</sub> , End | т7   | Wait, End                                        |      |                                           |

Gra = T5 · (add + addi) + T6 · st + T7 · shr + ...

• Use of datapath conditions

• Grc =  $T4 \cdot add + T4 \cdot (n=0) \cdot shr + ...$

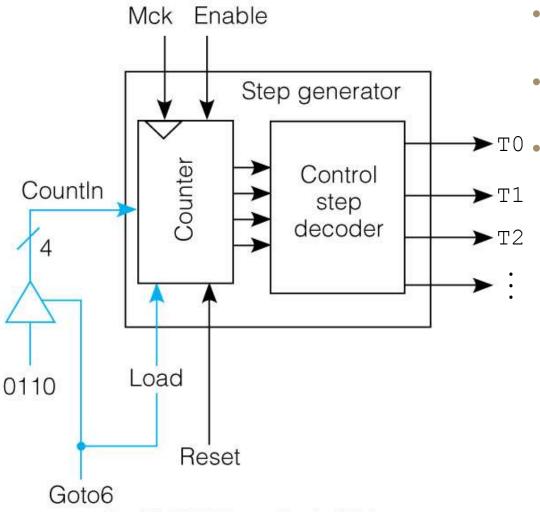

# Branching in the Control Unit

Copyright © 2004 Pearson Prentice Hall, Inc.

- Tri-state gates allow 6 to be applied to counter input

- Reset will synchronously reset counter to step To

- Mck is the master clock oscillator signal

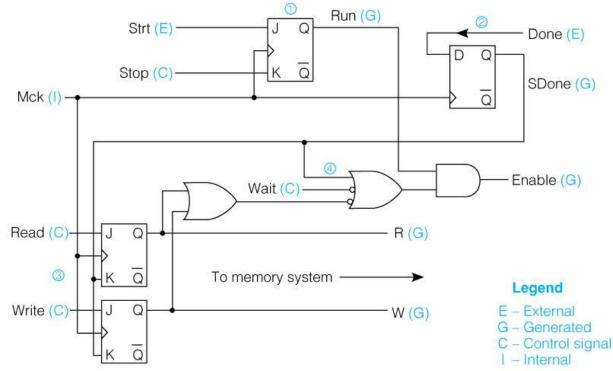

# Clocking Logic

- Generates Run signal

- Generate synchronized done signal SDone

- Generates R, W from Read, Write control

- Generates Enable which controls counter

# **Completed 1-Bus Design**

- High level architecture block diagram

- Concrete RTN steps

- Hardware design of registers and data path logic

- Revision of concrete RTN steps where needed

- Control sequences

- Register clocking decisions

- Logic equations for control signals

- Time step generator design

- Clock run, stop, and synchronization logic